16 層 PCB は、最新の電子デバイスに必要な複雑さと柔軟性を提供します。基板の最適なパフォーマンスを達成するには、積層順序と層間接続方法の熟練した設計と選択が重要です。この記事では、設計者やエンジニアが効率的で信頼性の高い 16 層回路基板を作成するのに役立つ考慮事項、ガイドライン、ベスト プラクティスについて説明します。

1.16 層 PCB の積層シーケンスの基本を理解する

1.1 積み重ね順序の定義と目的

積層順序とは、銅層や絶縁層などの材料を積層して多層回路基板を形成する配置と順序を指します。積層順序は、信号層、電源層、グランド層、およびその他の重要なコンポーネントの配置を決定します。スタック。

積層シーケンスの主な目的は、基板に必要な電気的および機械的特性を達成することです。これは、回路基板のインピーダンス、信号の完全性、配電、熱管理、製造の実現可能性を決定する上で重要な役割を果たします。積層順序は、ボードの全体的なパフォーマンス、信頼性、製造性に影響します。

1.2 スタッキングシーケンスの設計に影響する要因: スタッキングシーケンスを設計する際には、考慮すべき要因がいくつかあります。

16層PCB:

a) 電気的考慮事項:適切な信号の完全性、インピーダンス制御、および電磁干渉の低減を確保するには、信号、電源、およびグランド プレーンのレイアウトを最適化する必要があります。

b) 熱に関する考慮事項:電源プレーンとグランドプレーンの配置とサーマルビアの組み込みにより、熱が効果的に放散され、コンポーネントの最適な動作温度が維持されます。

c) 製造上の制約:選択する積層順序では、材料の入手可能性、層の数、ドリルのアスペクト比、そしてアライメント精度。

d) コストの最適化:材料、層の数、積層の複雑さの選択は、必要な性能と信頼性を確保しながら、プロジェクトの予算と一致する必要があります。

1.3 16 層回路基板の積層順序の一般的なタイプ: 16 層の一般的な積層順序がいくつかあります。

必要な性能と要件に応じて PCB を選択します。一般的な例としては次のようなものがあります。

a) 対称スタッキングシーケンス:このシーケンスでは、信号層を電源層とグランド層の間に対称的に配置して、良好な信号の完全性、最小限のクロストーク、バランスのとれた熱放散を実現します。

b) 順次スタッキングシーケンス:このシーケンスでは、信号層が電源層とグランド層の間に順番に配置されます。これにより、層の配置をより詳細に制御でき、特定の信号整合性要件を満たすのに役立ちます。

c) 混合積層順序:これには、対称的および連続的な積み重ね順序の組み合わせが含まれます。ボードの特定の部分のレイアップをカスタマイズおよび最適化できます。

d) 信号に敏感なスタッキングシーケンス:このシーケンスにより、ノイズ耐性と絶縁性が向上するため、敏感な信号層がグランド プレーンの近くに配置されます。

2.16 層 PCB 積層順序の選択に関する重要な考慮事項:

2.1 信号の完全性と電力の完全性に関する考慮事項:

積層順序は、ボードの信号の完全性と電源の完全性に大きな影響を与えます。信号の歪み、ノイズ、電磁干渉のリスクを最小限に抑えるには、信号プレーンと電源/グランド プレーンを適切に配置することが重要です。主な考慮事項は次のとおりです。

a) 信号層の配置:高速信号層は、低インダクタンスのリターンパスを提供し、ノイズ結合を最小限に抑えるために、グランドプレーンの近くに配置する必要があります。信号のスキューと長さの一致を最小限に抑えるために、信号層も慎重にレイアウトする必要があります。

b) 電源プレーンの分配:スタッキング シーケンスでは、電源の完全性をサポートするために適切な電源プレーンの分散を確保する必要があります。電圧降下、インピーダンスの不連続性、ノイズ結合を最小限に抑えるために、十分な電源プレーンとグランド プレーンを戦略的に配置する必要があります。

c) デカップリングコンデンサ:デカップリング コンデンサを適切に配置することは、適切な電力伝送を確保し、電源ノイズを最小限に抑えるために重要です。積層シーケンスでは、デカップリング コンデンサを電源プレーンとグランド プレーンに近づける必要があります。

2.2 熱管理と放熱:

効率的な熱管理は、回路基板の信頼性とパフォーマンスを確保するために重要です。積層順序では、電源プレーンとグランド プレーン、サーマル ビア、その他の冷却機構の適切な配置を考慮する必要があります。重要な考慮事項は次のとおりです。

a) 電源プレーンの分配:スタック全体に電源プレーンとグランドプレーンを適切に配置することで、影響を受けやすいコンポーネントから熱を逃がし、基板全体に均一な温度分布を確保します。

b) サーマルビア:積層順序では、内層から外層またはヒートシンクへの熱放散を促進するために、サーマルビアを効果的に配置できるようにする必要があります。これにより、局所的なホットスポットが防止され、効率的な熱放散が保証されます。

c) コンポーネントの配置:積み重ね順序では、過熱を避けるために加熱コンポーネントの配置と近接性を考慮する必要があります。ヒートシンクやファンなどの冷却機構とコンポーネントの適切な配置も考慮する必要があります。

2.3 製造上の制約とコストの最適化:

積層順序は、基板の実現可能性と手頃な価格に重要な役割を果たすため、製造上の制約とコストの最適化を考慮する必要があります。考慮事項は次のとおりです。

a) 材料の入手可能性:選択した積層順序は、材料の入手可能性および選択した PCB 製造プロセスとの適合性と一致している必要があります。

b) 層の数と複雑さ:積層順序は、層数、ドリルのアスペクト比、位置合わせ精度などの要素を考慮して、選択した PCB 製造プロセスの制約内で設計する必要があります。

c) コストの最適化:積層順序は、必要な性能と信頼性を損なうことなく、材料の使用を最適化し、製造の複雑さを軽減する必要があります。材料の無駄、プロセスの複雑さ、組み立てに関連するコストを最小限に抑えることを目指す必要があります。

2.4 レイヤーアライメントと信号クロストーク:

積層シーケンスでは、層の位置合わせの問題に対処し、信号の完全性に悪影響を与える可能性のある信号のクロストークを最小限に抑える必要があります。重要な考慮事項は次のとおりです。

a) 対称スタッキング:電源層とグランド層の間に信号層を対称的に積層することで、結合を最小限に抑え、クロストークを低減します。

b) 差動ペアの配線:高速差動信号を効率的に配線するには、積層シーケンスにより信号層を適切に配置できる必要があります。これにより、信号の完全性が維持され、クロストークが最小限に抑えられます。

c) 信号分離:スタッキングシーケンスでは、クロストークと干渉を減らすために、敏感なアナログ信号とデジタル信号の分離を考慮する必要があります。

2.5 インピーダンス制御と RF/マイクロ波の統合:

RF/マイクロ波アプリケーションの場合、適切なインピーダンス制御と統合を実現するには、積層順序が重要です。主な考慮事項は次のとおりです。

a) 制御されたインピーダンス:積層順序では、トレース幅、誘電体の厚さ、層配置などの要素を考慮して、制御されたインピーダンス設計が可能になる必要があります。これにより、RF/マイクロ波信号の正しい信号伝播とインピーダンス整合が保証されます。

b) 信号層の配置:RF/マイクロ波信号は、他の信号からの干渉を最小限に抑え、信号の伝播を向上させるために、外層の近くに戦略的に配置する必要があります。

c) RF シールド:積層順序には、RF/マイクロ波信号を干渉から分離して保護するために、グランド層とシールド層を適切に配置する必要があります。

3.層間の接続方法

3.1 スルーホール、止まり穴、埋め込み穴:

ビアは、プリント基板 (PCB) 設計において、異なる層を接続する手段として広く使用されています。これらは、PCB のすべての層を貫通するドリル穴であり、電気的導通を提供するためにメッキされています。スルーホールは強力な電気接続を提供し、作成と修理が比較的簡単です。ただし、より大きなドリルビットサイズが必要になるため、PCB 上の貴重なスペースが占有され、配線オプションが制限されます。

ブラインドビアと埋め込みビアは、スペース利用と配線の柔軟性において利点をもたらす代替層間接続方法です。

ブラインド ビアは PCB 表面からドリルで開けられ、すべての層を通過することなく内部層で終端します。これにより、より深い層には影響を与えずに、隣接する層間の接続が可能になります。これにより、基板スペースをより効率的に使用できるようになり、ドリル穴の数が減ります。一方、埋め込みビアは、PCB の内層内に完全に囲まれており、外層までは伸びていない穴です。これらは、外側の層に影響を与えることなく、内側の層間の接続を提供します。埋め込みビアは外層のスペースを占有しないため、スルーホールやブラインドビアよりもスペースを節約できるという大きな利点があります。

スルー ホール、ブラインド ビア、および埋め込みビアの選択は、PCB 設計の特定の要件によって異なります。スルーホールは通常、より単純な設計、または堅牢性と修復性が主な関心事である場合に使用されます。ハンドヘルド デバイス、スマートフォン、ラップトップなど、スペースが重要な要素である高密度設計では、ブラインド ビアや埋め込みビアが好まれます。

3.2 微細孔とHDIテクノロジー:

マイクロビアは、PCB に高密度の層間接続を提供する小さな直径の穴 (通常は 150 ミクロン未満) です。これらは、小型化、信号の完全性、配線の柔軟性において大きな利点をもたらします。

マイクロビアは、スルーホール マイクロビアとブラインド マイクロビアの 2 つのタイプに分類できます。マイクロビアは、PCB の上面からドリルで穴を開け、すべての層を貫通することによって構築されます。ブラインド マイクロビアは、その名前が示すように、特定の内部層にのみ拡張され、すべての層を貫通するわけではありません。

高密度相互接続 (HDI) は、マイクロビアと高度な製造技術を使用して、より高い回路密度とパフォーマンスを実現するテクノロジーです。 HDI テクノロジーにより、より小型のコンポーネントの配置とより緊密な配線が可能になり、その結果、フォーム ファクターが小さくなり、信号の完全性が向上します。 HDI テクノロジは、小型化、信号伝播の改善、信号歪みの低減、機能の強化という点で、従来の PCB テクノロジに比べていくつかの利点をもたらします。複数のマイクロビアを備えた多層設計が可能になるため、相互接続の長さが短縮され、寄生容量とインダクタンスが低減されます。

HDI テクノロジーにより、RF/マイクロ波アプリケーションに不可欠な高周波積層板や薄い誘電体層などの先進的な材料の使用も可能になります。より優れたインピーダンス制御を提供し、信号損失を低減し、信頼性の高い高速信号伝送を保証します。

3.3 層間接続の材料とプロセス:

層間接続の材料と技術の選択は、PCB の良好な電気的性能、機械的信頼性、製造性を確保するために重要です。一般的に使用される層間接続材料と技術には次のようなものがあります。

a) 銅:銅は、その優れた導電性とはんだ付け性により、PCB の導電層やビアに広く使用されています。通常、信頼性の高い電気接続を提供するために穴にメッキされます。

b) はんだ付け:ウェーブはんだ付けやリフローはんだ付けなどのはんだ付け技術は、PCB 上のスルーホールと他のコンポーネントの間の電気接続を行うためによく使用されます。ビアにはんだペーストを塗布し、熱を加えてはんだを溶かし、信頼性の高い接続を形成します。

c) 電気めっき:無電解銅めっきや電解銅などの電気めっき技術を使用してビアをめっきし、導電性を高め、良好な電気接続を確保します。

d) 結合:接着接合や熱圧着などの接合技術は、層状構造を接合し、信頼性の高い相互接続を作成するために使用されます。

e) 誘電体材料:PCB スタックアップの誘電体材料の選択は、層間接続にとって重要です。 FR-4 や Rogers ラミネートなどの高周波ラミネートは、信号の完全性を確保し、信号損失を最小限に抑えるためによく使用されます。

3.4 断面デザインとその意味:

PCB スタックアップの断面設計により、層間の接続の電気的および機械的特性が決まります。断面設計に関する主な考慮事項は次のとおりです。

a) 層の配置:PCB スタックアップ内の信号、電源、およびグランド プレーンの配置は、信号の完全性、電源の完全性、および電磁干渉 (EMI) に影響します。信号層を電源プレーンおよびグランドプレーンと適切に配置および配置することで、ノイズ結合を最小限に抑え、低インダクタンスのリターンパスを確保できます。

b) インピーダンス制御:断面設計では、特に高速デジタル信号または RF/マイクロ波信号の場合、制御されたインピーダンス要件を考慮する必要があります。これには、所望の特性インピーダンスを達成するための誘電体材料と厚さの適切な選択が含まれます。

c) 熱管理:断面設計では、効果的な放熱と熱管理を考慮する必要があります。電源プレーンとグランドプレーン、サーマルビア、冷却機構を備えたコンポーネント (ヒートシンクなど) を適切に配置すると、熱が放散され、最適な動作温度が維持されます。

d) 機械的信頼性:セクション設計では、特に熱サイクルや機械的ストレスにさらされる可能性のある用途では、機械的信頼性を考慮する必要があります。材料、接合技術、スタックアップ構成を適切に選択することで、PCB の構造的完全性と耐久性が確保されます。

4.16層PCBの設計ガイドライン

4.1 層の割り当てと分散:

16 層の回路基板を設計する場合、性能と信号の整合性を最適化するために層を慎重に割り当てて分散することが重要です。層の割り当てに関するガイドラインは次のとおりです

そして配布:

必要な信号層の数を決定します。

回路設計の複雑さと、配線する必要がある信号の数を考慮してください。必要なすべての信号に対応するのに十分な信号層を割り当て、適切な配線スペースを確保し、過剰な配線を回避します。混雑。グランド プレーンと電源プレーンを割り当てます。

少なくとも 2 つの内部層をグランド プレーンと電源プレーンに割り当てます。グランドプレーンは、信号の安定した基準を提供し、電磁干渉 (EMI) を最小限に抑えるのに役立ちます。電源プレーンは、電圧降下を最小限に抑えるのに役立つ低インピーダンスの配電ネットワークを提供します。

敏感な信号層を分離します。

アプリケーションによっては、干渉やクロストークを防ぐために、敏感な信号層や高速信号層をノイズの多い層や高電力層から分離する必要がある場合があります。これは、専用のグランド プレーンまたは電源プレーンをそれらの間に配置するか、絶縁層を使用することによって実行できます。

信号層を均等に分散します。

信号層を基板スタックアップ全体に均等に分散させて、隣接する信号間の結合を最小限に抑え、信号の整合性を維持します。層間クロストークを最小限に抑えるために、同じスタックアップ領域に信号層を隣接して配置しないようにします。

高周波信号を考えてみましょう。

設計に高周波信号が含まれている場合は、伝送線路の影響を最小限に抑え、伝播遅延を減らすために、高周波信号層を外側の層の近くに配置することを検討してください。

4.2 ルーティングと信号ルーティング:

適切な信号の完全性を確保し、干渉を最小限に抑えるには、ルーティングと信号トレースの設計が重要です。 16 層回路基板のレイアウトと信号配線に関するガイドラインをいくつか示します。

高電流信号には幅広のトレースを使用します。

電源接続やグランド接続など、大電流が流れる信号の場合は、抵抗と電圧降下を最小限に抑えるために幅の広い配線を使用します。

高速信号のインピーダンス整合:

高速信号の場合、反射や信号の減衰を防ぐために、トレースのインピーダンスが伝送線路の特性インピーダンスと一致していることを確認してください。制御されたインピーダンス設計手法を使用し、配線幅を正確に計算します。

トレースの長さとクロスオーバーポイントを最小限に抑えます。

配線の長さをできるだけ短くし、クロスオーバーポイントの数を減らして、寄生容量、インダクタンス、干渉を低減します。コンポーネントの配置を最適化し、専用の配線層を使用して、長く複雑なトレースを回避します。

高速信号と低速信号を分離する:

高速信号と低速信号を分離し、高速信号へのノイズの影響を最小限に抑えます。高速信号を専用の信号層に配置し、高電力コンポーネントやノイズの多いコンポーネントから遠ざけます。

高速信号には差動ペアを使用します。

ノイズを最小限に抑え、高速差動信号の信号整合性を維持するには、差動ペア配線技術を使用します。信号のスキューやクロストークを防ぐために、差動ペアのインピーダンスと長さを一致させてください。

4.3 グランド層と電源層の分布:

良好な電力整合性を実現し、電磁干渉を軽減するには、グランド プレーンと電源プレーンを適切に配置することが重要です。 16 層回路基板上のグランドおよび電源プレーンの割り当てに関するガイドラインをいくつか示します。

専用のグランド プレーンと電源プレーンを割り当てます。

専用のグランド プレーンと電源プレーンに少なくとも 2 つの内部層を割り当てます。これにより、グランド ループが最小限に抑えられ、EMI が低減され、高周波信号に低インピーダンスのリターン パスが提供されます。

デジタルとアナログの個別のグランドプレーン:

設計にデジタル セクションとアナログ セクションがある場合は、セクションごとに個別のグランド プレーンを設けることをお勧めします。これにより、デジタルセクションとアナログセクション間のノイズカップリングが最小限に抑えられ、信号の完全性が向上します。

グランド プレーンと電源プレーンを信号プレーンの近くに配置します。

グランド プレーンと電源プレーンを、それらが供給する信号プレーンの近くに配置して、ループ領域を最小限に抑え、ノイズの拾い込みを低減します。

電源プレーンに複数のビアを使用します。

複数のビアを使用して電源プレーンを接続し、電力を均等に分配し、電源プレーンのインピーダンスを低減します。これにより、電源電圧降下が最小限に抑えられ、電源の完全性が向上します。

電源プレーンの狭いネックを回避します。

電源プレーンの狭いネックは電流の集中を引き起こし、抵抗を増加させ、電圧降下や電源プレーンの非効率を引き起こす可能性があるため避けてください。異なる電源プレーン領域間で強力な接続を使用します。

4.4 サーマルパッドとビアの配置:

熱を効果的に放散し、コンポーネントの過熱を防ぐには、サーマル パッドとビアを適切に配置することが重要です。 16 層回路基板上のサーマル パッドとビアの配置に関するガイドラインをいくつか示します。

サーマルパッドを発熱コンポーネントの下に置きます。

発熱コンポーネント (パワーアンプや高出力 IC など) を特定し、その直下にサーマルパッドを配置します。これらのサーマル パッドは、内部のサーマル レイヤーに熱を伝達するための直接的な熱経路を提供します。

熱放散のために複数のサーマルビアを使用します。

複数のサーマルビアを使用してサーマル層と外層を接続し、効率的な熱放散を実現します。これらのビアをサーマルパッドの周囲に千鳥状に配置して、均一な熱分布を実現できます。

熱インピーダンスと層の積層を考慮します。

サーマルビアを設計するときは、基板の材料と層の積層の熱インピーダンスを考慮してください。ビアのサイズと間隔を最適化して、熱抵抗を最小限に抑え、熱放散を最大化します。

4.5 コンポーネントの配置と信号の整合性:

コンポーネントを適切に配置することは、信号の整合性を維持し、干渉を最小限に抑えるために重要です。 16 層回路基板にコンポーネントを配置するためのガイドラインをいくつか示します。

グループ関連コンポーネント:

同じサブシステムの一部であるか、強い電気的相互作用がある関連コンポーネントをグループ化します。これにより、配線の長さが短縮され、信号の減衰が最小限に抑えられます。

高速コンポーネントを近くに置いてください。

高周波発振器やマイクロコントローラーなどの高速コンポーネントを互いに近づけて配置し、配線長を最小限に抑え、適切な信号の整合性を確保します。

重要な信号のトレース長を最小限に抑えます。

重要な信号のトレース長を最小限に抑えて、伝播遅延と信号の減衰を低減します。これらのコンポーネントをできるだけ近くに配置します。

機密性の高いコンポーネントを分離します。

アナログ コンポーネントや低レベル センサーなどのノイズに敏感なコンポーネントを高電力コンポーネントやノイズの多いコンポーネントから分離して、干渉を最小限に抑え、信号の整合性を維持します。

デカップリング コンデンサを検討してください。

デカップリング コンデンサを各コンポーネントの電源ピンのできるだけ近くに配置して、クリーンな電力を供給し、電圧変動を最小限に抑えます。これらのコンデンサは、電源を安定させ、ノイズ結合を軽減するのに役立ちます。

5.スタックアップ設計のためのシミュレーションおよび解析ツール

5.1 3D モデリングおよびシミュレーション ソフトウェア:

3D モデリングおよびシミュレーション ソフトウェアは、設計者が PCB スタックアップの仮想表現を作成できるため、スタックアップ設計にとって重要なツールです。このソフトウェアは、レイヤー、コンポーネント、およびそれらの物理的な相互作用を視覚化できます。スタックアップをシミュレーションすることで、設計者は信号クロストーク、EMI、機械的制約などの潜在的な問題を特定できます。また、コンポーネントの配置を検証し、PCB 設計全体を最適化するのにも役立ちます。

5.2 シグナルインテグリティ解析ツール:

シグナルインテグリティ解析ツールは、PCB スタックアップの電気的性能を解析し、最適化するために重要です。これらのツールは、数学的アルゴリズムを使用して、インピーダンス制御、信号反射、ノイズ結合などの信号の動作をシミュレートおよび分析します。シミュレーションと解析を実行することで、設計者は設計プロセスの早い段階で潜在的な信号整合性の問題を特定し、信頼性の高い信号伝送を確保するために必要な調整を行うことができます。

5.3 熱分析ツール:

熱解析ツールは、PCB の熱管理を解析および最適化することで、スタックアップ設計において重要な役割を果たします。これらのツールは、スタックの各層内の熱放散と温度分布をシミュレートします。消費電力と熱伝達経路を正確にモデル化することで、設計者はホットスポットを特定し、銅層とサーマルビアの配置を最適化し、重要なコンポーネントの適切な冷却を確保できます。

5.4 製造可能性を考慮した設計:

製造容易性を考慮した設計は、スタックアップ設計の重要な側面です。選択したスタックアップを効率的に製造できるようにするためのさまざまなソフトウェア ツールが利用可能です。これらのツールは、材料の入手可能性、層の厚さ、製造プロセス、製造コストなどの要素を考慮して、目的のスタックアップを達成する実現可能性に関するフィードバックを提供します。これらは、設計者が情報に基づいてスタッキングを最適化して製造を簡素化し、遅延のリスクを軽減し、歩留まりを向上させる決定を下すのに役立ちます。

6.16 層 PCB の段階的な設計プロセス

6.1 初期要件の収集:

このステップでは、16 層 PCB 設計に必要な要件をすべて収集します。 PCB の機能、必要な電気的性能、機械的制約、および従う必要がある特定の設計ガイドラインや規格を理解します。

6.2 コンポーネントの割り当てと配置:

要件に応じて、PCB 上に部品を配置し、その配置を決定します。信号の完全性、熱に関する考慮事項、機械的制約などの要素を考慮してください。電気的特性に基づいてコンポーネントをグループ化し、ボード上に戦略的に配置して干渉を最小限に抑え、信号の流れを最適化します。

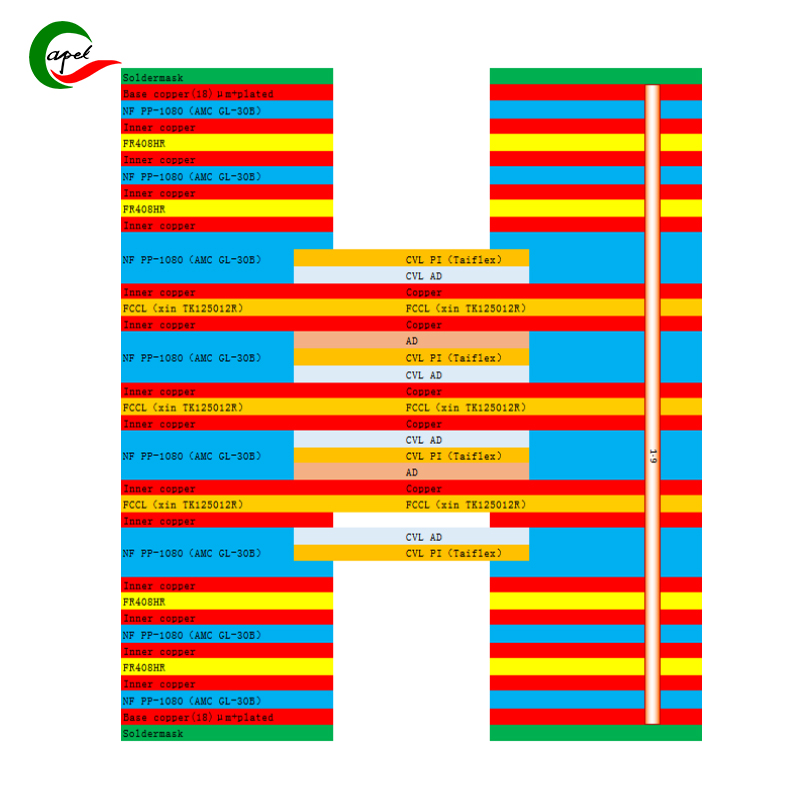

6.3 スタックアップ設計と層分布:

16 層 PCB のスタックアップ設計を決定します。適切な材料を選択するには、誘電率、熱伝導率、コストなどの要素を考慮してください。電気的要件に従って、信号、電源、およびグランド プレーンを割り当てます。バランスのとれたスタックを確保し、信号の整合性を向上させるために、グランド プレーンと電源プレーンを対称的に配置します。

6.4 信号ルーティングとルーティングの最適化:

このステップでは、適切なインピーダンス制御、信号の完全性を確保し、信号のクロストークを最小限に抑えるために、信号トレースがコンポーネント間で配線されます。ルーティングを最適化して重要な信号の長さを最小限に抑え、敏感なトレースの交差を回避し、高速信号と低速信号の分離を維持します。必要に応じて、差動ペアと制御されたインピーダンス配線技術を使用します。

6.5 層間接続とビアの配置:

層間の接続ビアの配置を計画します。層の遷移やコンポーネントの接続に基づいて、スルー ホールやブラインド ホールなどの適切なビア タイプを決定します。ビアのレイアウトを最適化して、信号の反射、インピーダンスの不連続性を最小限に抑え、PCB 上の均一な分布を維持します。

6.6 最終設計の検証とシミュレーション:

製造前に、最終設計の検証とシミュレーションが実行されます。シミュレーション ツールを使用して、シグナル インテグリティ、パワー インテグリティ、熱挙動、および製造可能性について PCB 設計を分析します。初期要件に照らして設計を検証し、パフォーマンスを最適化し、製造可能性を確保するために必要な調整を行います。

設計プロセス全体を通じて、電気エンジニア、機械エンジニア、製造チームなどの他の関係者と協力してコミュニケーションをとり、すべての要件が満たされ、潜在的な問題が解決されることを確認します。定期的に設計をレビューして反復し、フィードバックと改善を組み込んでください。

7.業界のベストプラクティスとケーススタディ

7.1 16 層 PCB 設計の成功例:

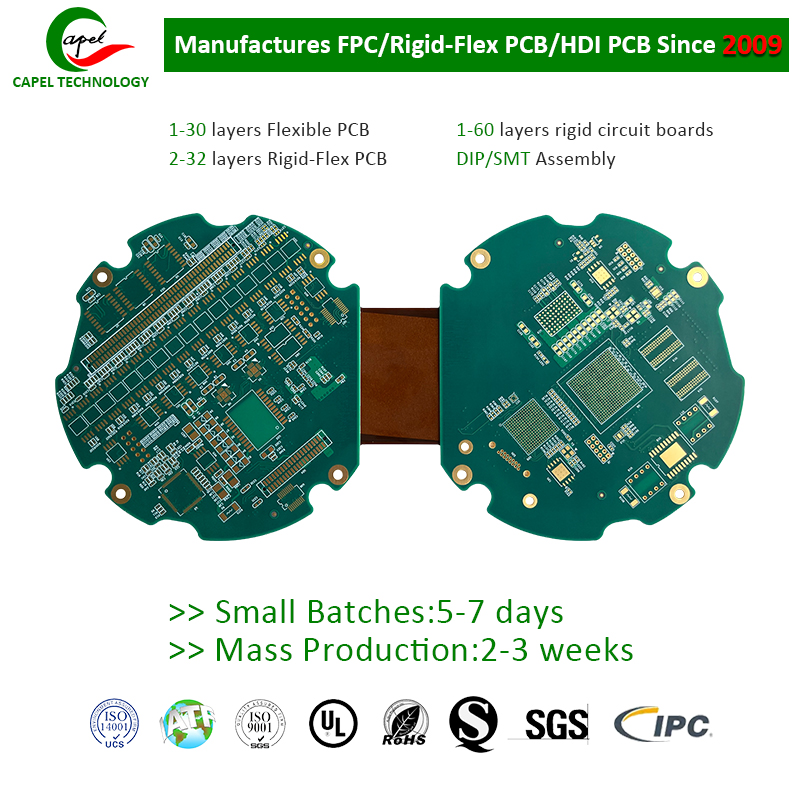

ケーススタディ 1:Shenzhen Capel Technology Co., Ltd. は、高速ネットワーク機器用の 16 層 PCB の設計に成功しました。信号の完全性と電力配分を慎重に考慮することで、優れたパフォーマンスを実現し、電磁干渉を最小限に抑えます。成功の鍵は、制御されたインピーダンス配線技術を使用した完全に最適化されたスタックアップ設計です。

ケーススタディ 2:Shenzhen Capel Technology Co., Ltd. は、複雑な医療機器用の 16 層 PCB を設計しました。表面実装コンポーネントとスルーホールコンポーネントを組み合わせて使用することで、コンパクトでありながら強力な設計を実現しました。慎重なコンポーネントの配置と効率的な配線により、優れた信号の整合性と信頼性が保証されます。

7.2 失敗から学び、落とし穴を避ける:

ケーススタディ 1:一部の PCB メーカーは、通信機器の 16 層 PCB 設計においてシグナル インテグリティの問題に遭遇しました。失敗の原因は、インピーダンス制御の考慮が不十分であったことと、適切なグランドプレーン分布がなかったことです。得られた教訓は、シグナルインテグリティ要件を注意深く分析し、厳格なインピーダンス制御設計ガイドラインを適用することです。

ケーススタディ 2:一部の PCB メーカーは、設計の複雑さにより 16 層 PCB の製造上の課題に直面していました。ブラインドビアや高密度に実装されたコンポーネントを過剰に使用すると、製造や組み立てが困難になります。学んだ教訓は、選択した PCB メーカーの能力を考慮して、設計の複雑さと製造可能性のバランスをとることです。

16 層 PCB 設計における落とし穴や落とし穴を回避するには、次のことが重要です。

a.設計の要件と制約を十分に理解します。

b.信号の完全性と電力分配を最適化するスタック構成。 c.パフォーマンスを最適化し、製造を簡素化するために、コンポーネントを慎重に分散および配置します。

d. インピーダンスの制御やブラインドビアの過剰な使用の回避など、適切な配線技術を確保します。

e.電気エンジニアや機械エンジニア、製造チームなど、設計プロセスに関与するすべての関係者と協力し、効果的にコミュニケーションをとる。

f.包括的な設計検証とシミュレーションを実行して、製造前に潜在的な問題を特定して修正します。

投稿日時: 2023 年 9 月 26 日

戻る